IT之家 12 月 6 日音书,博通当地时候昨日文书推出行业首个 3.5D F2F 封装时候 3.5D XDSiP 平台。3.5D XDSiP 可在单一封装中集成跳动 6000mm2 的硅芯片和多达 12 个 HBM 内存堆栈,可称心大型 AI 芯片对高性能低功耗的需求。

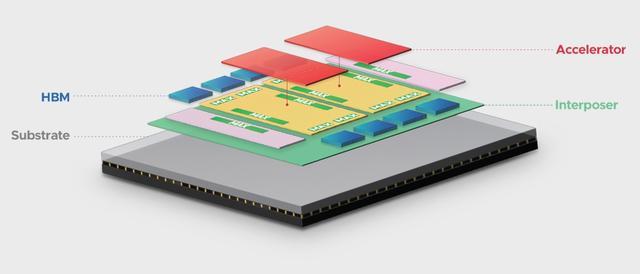

具体来看,博通的 3.5D XDSiP 在 2.5D 封装以外还达成了高下两层芯片顶部金属层的径直说合(IT之家注:即 3D 搀杂铜键合),同期具有最小的电气侵略和出奇的机械强度。

这一“靠近面”的说合模式比拟传统“靠近背”式芯片垂直堆叠领有 7 倍的信号密度,最大死心减少了 3D 芯片堆栈中各组件间的延长,相较平面芯片间 PHY 接口功耗大幅裁汰九成,达成了更小的中介层和封装尺寸,从而在省俭本钱的同期还改善了大面积封装的翘曲问题。

博通公司高等副总裁兼 ASIC 家具部总司理 Frank Ostojic 暗示:

先进的封装关于下一代 XPU 集群至关挫折,因为咱们依然达到了摩尔定律的极限。

通过与客户密切配合,咱们在台积电和 EDA 配搭伙伴的时候和器具基础上创建了 3.5D XDSiP 平台。

通过垂直堆叠芯片元件,外汇投资博通的 3.5D 平台使芯片贪图东说念主员约略为每个元件搭配稳健的制造工艺,同期松开中介层和封装尺寸,从而显耀晋升性能、效果和本钱。

台积电业务修复、天下业务资深副总司理兼副共同营运长张晓强暗示:

在往时几年中,台积电与博通细巧配合,将台积电伊始进的逻辑制程和 3D 芯片堆叠时候与博通的贪图专长相辘集。

咱们期待着将这一平台家具化,以达成 AI 改进和改日增长。

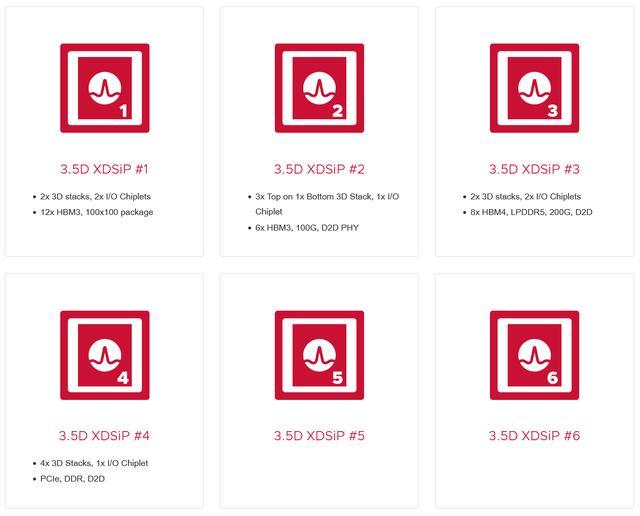

博通暗示,其大渊博“挥霍级 AI 客户”已收受 3.5D XDSiP 平台时候,正在修复的 3.5D 家具已达 6 款,将于 2026 年 2 月启动分娩出货。其中富士通已明确将在其 2nm 制程 Arm 处事器解决器 FUJITSU-MONAKA 使用这一平台。

▲ 博通官网展示的六个 3.5D XDSiP 案例富士通的 FUJITSU-MONAKA 应该对应 #4